依照上述每一次按"Start Compilation"後,需要經過Verilog程式編譯 > 電路合成 > 訊號模擬,需要花費很多時間,下列的步驟只有先分析電路後,直接做RTL模擬,加快程式除錯的時間。

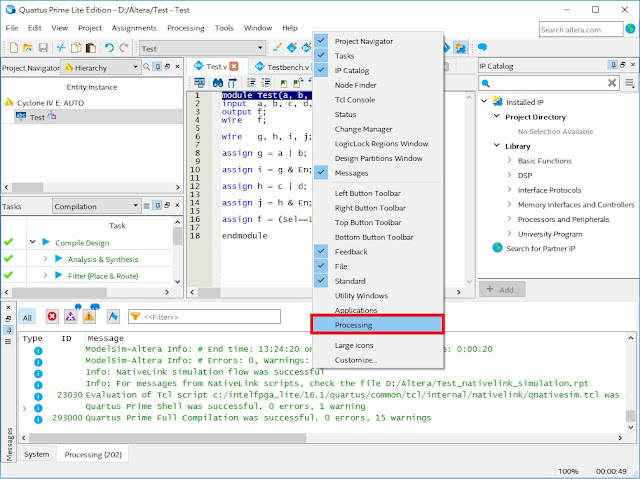

(1). 將滑鼠游標移至工具列,按"滑鼠右鍵",勾選"Processing"。

(2). 增加了工具列的ICON。

(3). 當模組電路與Test bench撰寫好後,點選"Analyze Current File",會將程式存檔,並進行電路分析。

(4). 電路分析沒有出現錯誤,如果有合成過,就點選"RTL Simulation",沒有合成過,就點選"Gate Level Simulation",此時軟體會開啟ModelSim。

依據上個步驟只有點選"Analyze Current File",分析設計的電路是否正確,哪這一步因該要點選"Gate Level Simulation"。

(5). 最後顯示其電路模擬的波形。

紅線: "x"狀態表示不定值。

藍線: "hi-z"狀態表示高阻抗。

綠線: 0、1狀態表示IO輸出值。

白色虛線: pu狀態表示外部模擬拉高電位。

沒有留言:

張貼留言