程式中使用的"#define Dummy 0x00"設定,是因為SPI的Clock是由MCU產生,STM8S是標準4線式的SPI介面,SI與SO pin可以同時做輸入與輸出的動作,當要使用SPI介面讀取其他IC的值時只要給MCU的"SPI->DR"暫存器一個Dummy的值就會產生SPI Read時所需要的Clock。

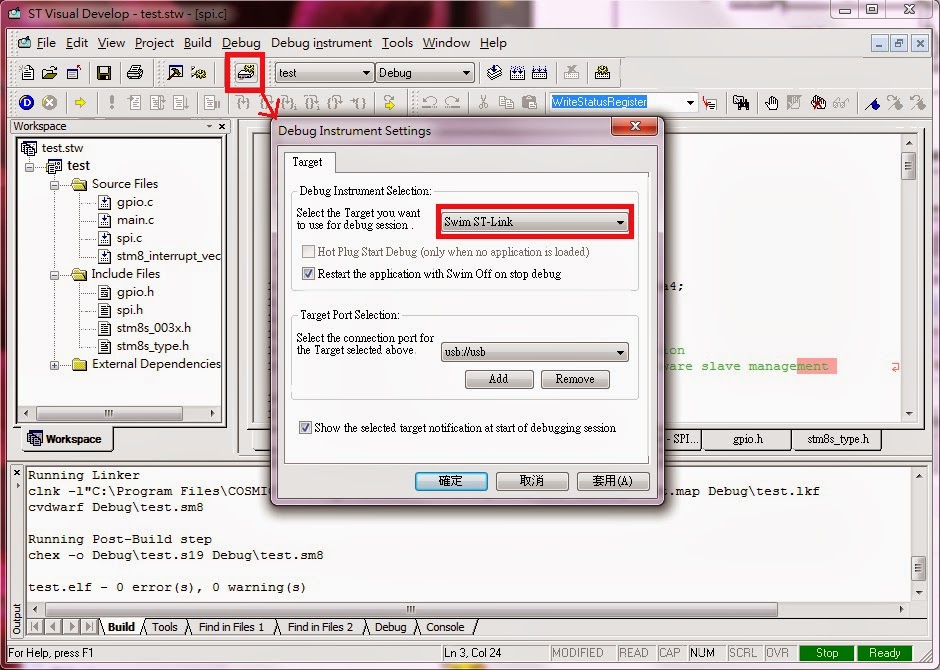

1. 整個project的程式檔案目錄如下圖所示.

2. main.c

/***********************************************/#include "stm8s_003x.h"

#include "stm8s_type.h"

#include "gpio.h"

#include "spi.h"

#define Dummy 0x00 //for SPI Clock

u8 ReadData;

int main(void)

{

enableInterrupts(); //InterruptInit

GPIOE_Init();

SPI_Init();

GPIOE->ODR &= ~(0x20); //NSS(CS) pull low.

SPI_IO(0xAA); //SPI write data

ReadData = SPI_IO(Dummy); //SPI read data

GPIOE->ODR |= 0x20; //NSS(CS) pull high.

return 0;

}

/***********************************************/

3. gpio.c

/***********************************************/#include "stm8s_003x.h"

#include "stm8s_type.h"

#include "gpio.h"

void GPIOE_Init(void)

{

GPIOE->DDR |= 0x20;

GPIOE->CR1 |= 0x20;

GPIOE->CR2 |= 0x00;

}

/***********************************************/

4. spi.c

/***********************************************/#include "stm8s_003x.h"

#include "stm8s_type.h"

#include "spi.h"

void SPI_Init(void)

{

SPI->CR1 |= 0x07; //Master configuration

SPI->CR2 |= 0x03; //Master mode, Software slave management enabled.

SPI->CR1 |= 0x40; //SPI enable

GPIOE->ODR |= 0x20; //NSS(CS) pull high.

}

u8 SPI_IO(u8 OutputData)

{

u8 InputData;

while(! (SPI->SR & 0x02)); //Transmit buffer empty.

SPI->DR = OutputData; //Output Data.

while(! (SPI->SR & 0x01)); //Receive buffer not empty.

InputData = SPI->DR; //Input Data.

return InputData; //Input Data.

}

/***********************************************/

5. stm8_interrupt_vector.c

/***********************************************//* BASIC INTERRUPT VECTOR TABLE FOR STM8 devices

* Copyright (c) 2007 STMicroelectronics

*/

typedef void @far (*interrupt_handler_t)(void);

struct interrupt_vector {

unsigned char interrupt_instruction;

interrupt_handler_t interrupt_handler;

};

@far @interrupt void NonHandledInterrupt (void)

{

/* in order to detect unexpected events during development,

it is recommended to set a breakpoint on the following instruction

*/

return;

}

extern void _stext(); /* startup routine */

struct interrupt_vector const _vectab[] = {

{0x82, (interrupt_handler_t)_stext}, /* reset */

{0x82, NonHandledInterrupt}, /* trap */

{0x82, NonHandledInterrupt}, /* irq0 */

{0x82, NonHandledInterrupt}, /* irq1 */

{0x82, NonHandledInterrupt}, /* irq2 */

{0x82, NonHandledInterrupt}, /* irq3 */

{0x82, NonHandledInterrupt}, /* irq4 */

{0x82, NonHandledInterrupt}, /* irq5 */

{0x82, NonHandledInterrupt}, /* irq6 */

{0x82, NonHandledInterrupt}, /* irq7 */

{0x82, NonHandledInterrupt}, /* irq8 */

{0x82, NonHandledInterrupt}, /* irq9 */

{0x82, NonHandledInterrupt}, /* irq10 */

{0x82, NonHandledInterrupt}, /* irq11 */

{0x82, NonHandledInterrupt}, /* irq12 */

{0x82, NonHandledInterrupt}, /* irq13 */

{0x82, NonHandledInterrupt}, /* irq14 */

{0x82, NonHandledInterrupt}, /* irq15 */

{0x82, NonHandledInterrupt}, /* irq16 */

{0x82, NonHandledInterrupt}, /* irq17 */

{0x82, NonHandledInterrupt}, /* irq18 */

{0x82, NonHandledInterrupt}, /* irq19 */

{0x82, NonHandledInterrupt}, /* irq20 */

{0x82, NonHandledInterrupt}, /* irq21 */

{0x82, NonHandledInterrupt}, /* irq22 */

{0x82, NonHandledInterrupt}, /* irq23 */

{0x82, NonHandledInterrupt}, /* irq24 */

{0x82, NonHandledInterrupt}, /* irq25 */

{0x82, NonHandledInterrupt}, /* irq26 */

{0x82, NonHandledInterrupt}, /* irq27 */

{0x82, NonHandledInterrupt}, /* irq28 */

{0x82, NonHandledInterrupt}, /* irq29 */

};

/***********************************************/

6. gpio.h

/***********************************************/#include "stm8s_type.h"

void GPIOE_Init(void);

/***********************************************/

7. spi.h

/***********************************************/#include "stm8s_type.h"

void SPI_Init(void);

u8 SPI_IO(u8 OutputData);

/***********************************************/

8. stm8s_003x.h

/***********************************************//* Define to prevent recursive inclusion -------------------------------------*/

#ifndef __STM8_003x_H

#define __STM8_003x_H

#include "stm8s_type.h"

/******************************************************************************/

/* Library configuration section */

/******************************************************************************/

/******************************************************************************/

/* Peripherals Base Address */

/******************************************************************************/

#define GPIOA_BaseAddress 0x5000

#define GPIOB_BaseAddress 0x5005

#define GPIOC_BaseAddress 0x500A

#define GPIOD_BaseAddress 0x500F

#define GPIOE_BaseAddress 0x5014

#define GPIOF_BaseAddress 0x5019

#define FLASH_BaseAddress 0x505A

#define ITC_BaseAddress 0x50A0

#define RST_BaseAddress 0x50B3

#define CLK_BaseAddress 0x50C3

#define WWDG_BaseAddress 0x50D1

#define IWDG_BaseAddress 0x50E0

#define AWU_BaseAddress 0x50F0

#define BEEP_BaseAddress 0x50F3

#define SPI_BaseAddress 0x5200

#define I2C_BaseAddress 0x5210

#define UART1_BaseAddress 0x5230

#define TIM1_BaseAddress 0x5250

#define TIM2_BaseAddress 0x5300

#define TIM4_BaseAddress 0x5340

#define ADC1_BaseAddress 0x53E0

/******************************************************************************/

/* Peripherals declarations */

/******************************************************************************/

#define GPIOA ((GPIO_TypeDef *) GPIOA_BaseAddress)

#define GPIOB ((GPIO_TypeDef *) GPIOB_BaseAddress)

#define GPIOC ((GPIO_TypeDef *) GPIOC_BaseAddress)

#define GPIOD ((GPIO_TypeDef *) GPIOD_BaseAddress)

#define GPIOE ((GPIO_TypeDef *) GPIOE_BaseAddress)

#define GPIOF ((GPIO_TypeDef *) GPIOF_BaseAddress)

#define FLASH ((FLASH_TypeDef *) FLASH_BaseAddress)

#define ITC ((ITC_TypeDef *) ITC_BaseAddress)

#define RST ((RST_TypeDef *) RST_BaseAddress)

#define CLK ((CLK_TypeDef *) CLK_BaseAddress)

#define WWDG ((WWDG_TypeDef *) WWDG_BaseAddress)

#define IWDG ((IWDG_TypeDef *) IWDG_BaseAddress)

#define AWU ((AWU_TypeDef *) AWU_BaseAddress)

#define BEEP ((BEEP_TypeDef *) BEEP_BaseAddress)

#define SPI ((SPI_TypeDef *) SPI_BaseAddress)

#define I2C ((I2C_TypeDef *) I2C_BaseAddress)

#define UART1 ((UART1_TypeDef *) UART1_BaseAddress)

#define TIM1 ((TIM1_TypeDef *) TIM1_BaseAddress)

#define TIM2 ((TIM2_TypeDef *) TIM2_BaseAddress)

#define TIM4 ((TIM4_TypeDef *) TIM4_BaseAddress)

#define ADC1 ((ADC1_TypeDef *) ADC1_BaseAddress)

/******************************************************************************/

/* IP registers structures */

/******************************************************************************/

#define enableInterrupts() {_asm("rim\n");} /* enable interrupts */

#define disableInterrupts() {_asm("sim\n");} /* disable interrupts */

/* @brief General Purpose I/Os (GPIO) */

typedef struct GPIO_struct

{

vu8 ODR; /*!< Output Data Register */

vu8 IDR; /*!< Input Data Register */

vu8 DDR; /*!< Data Direction Register */

vu8 CR1; /*!< Configuration Register 1 */

vu8 CR2; /*!< Configuration Register 2 */

}GPIO_TypeDef;

/* @brief Serial Peripheral Interface (SPI) */

typedef struct SPI_struct

{

vu8 CR1; /*!< SPI control register 1 */

vu8 CR2; /*!< SPI control register 2 */

vu8 ICR; /*!< SPI interrupt control register */

vu8 SR; /*!< SPI status register */

vu8 DR; /*!< SPI data I/O register */

vu8 CRCPR; /*!< SPI CRC polynomial register */

vu8 RXCRCR; /*!< SPI Rx CRC register */

vu8 TXCRCR; /*!< SPI Tx CRC register */

}SPI_TypeDef;

#endif /* __STM8S_003x_H */

/******************* (C) COPYRIGHT 2009 STMicroelectronics *****END OF FILE****/

9. stm8s_type.h

/***********************************************//**

******************************************************************************

* @file stm8s_type.h

* @brief This file contains all common data types.

* @author STMicroelectronics - MCD Application Team

* @version V1.1.1

* @date 06/05/2009

******************************************************************************

*

* THE PRESENT FIRMWARE WHICH IS FOR GUIDANCE ONLY AIMS AT PROVIDING CUSTOMERS

* WITH CODING INFORMATION REGARDING THEIR PRODUCTS IN ORDER FOR THEM TO SAVE

* TIME. AS A RESULT, STMICROELECTRONICS SHALL NOT BE HELD LIABLE FOR ANY

* DIRECT, INDIRECT OR CONSEQUENTIAL DAMAGES WITH RESPECT TO ANY CLAIMS ARISING

* FROM THE CONTENT OF SUCH FIRMWARE AND/OR THE USE MADE BY CUSTOMERS OF THE

* CODING INFORMATION CONTAINED HEREIN IN CONNECTION WITH THEIR PRODUCTS.

*

* <h2><center>© COPYRIGHT 2009 STMicroelectronics</center></h2>

* @image html logo.bmp

******************************************************************************

*/

/* Define to prevent recursive inclusion -------------------------------------*/

#ifndef __STM8S_TYPE_H

#define __STM8S_TYPE_H

/* Includes ------------------------------------------------------------------*/

/* Exported types ------------------------------------------------------------*/

typedef signed long s32;

typedef signed short s16;

typedef signed char s8;

typedef signed long const sc32; /* Read Only */

typedef signed short const sc16; /* Read Only */

typedef signed char const sc8; /* Read Only */

typedef volatile signed long vs32;

typedef volatile signed short vs16;

typedef volatile signed char vs8;

typedef volatile signed long const vsc32; /* Read Only */

typedef volatile signed short const vsc16; /* Read Only */

typedef volatile signed char const vsc8; /* Read Only */

typedef unsigned long u32;

typedef unsigned short u16;

typedef unsigned char u8;

typedef unsigned long const uc32; /* Read Only */

typedef unsigned short const uc16; /* Read Only */

typedef unsigned char const uc8; /* Read Only */

typedef volatile unsigned long vu32;

typedef volatile unsigned short vu16;

typedef volatile unsigned char vu8;

typedef volatile unsigned long const vuc32; /* Read Only */

typedef volatile unsigned short const vuc16; /* Read Only */

typedef volatile unsigned char const vuc8; /* Read Only */

typedef enum

{

FALSE = 0,

TRUE = !FALSE

}bool;

typedef enum

{

RESET = 0,

SET = !RESET

}FlagStatus, ITStatus, BitStatus;

typedef enum

{

DISABLE = 0,

ENABLE = !DISABLE

}FunctionalState;

#define IS_FUNCTIONALSTATE_OK(VALUE) ( (VALUE == ENABLE) || (VALUE == DISABLE) )

typedef enum

{

ERROR = 0,

SUCCESS = !ERROR

}ErrorStatus;

#define U8_MAX ((u8)255)

#define S8_MAX ((s8)127)

#define S8_MIN ((s8)-128)

#define U16_MAX ((u16)65535u)

#define S16_MAX ((s16)32767)

#define S16_MIN ((s16)-32768)

#define U32_MAX ((u32)4294967295uL)

#define S32_MAX ((s32)2147483647)

#define S32_MIN ((s32)-2147483648)

/* Exported constants --------------------------------------------------------*/

/* Exported macro ------------------------------------------------------------*/

/* Exported functions ------------------------------------------------------- */

#endif /* __STM8S_TYPE_H */

/******************* (C) COPYRIGHT 2009 STMicroelectronics *****END OF FILE****/

/***********************************************/