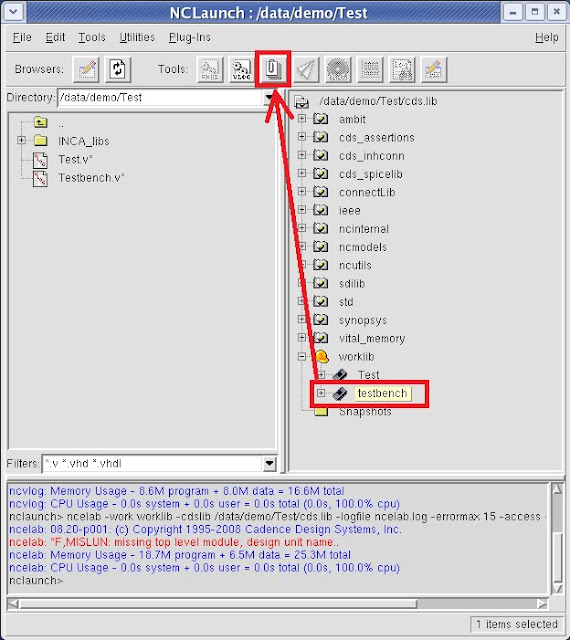

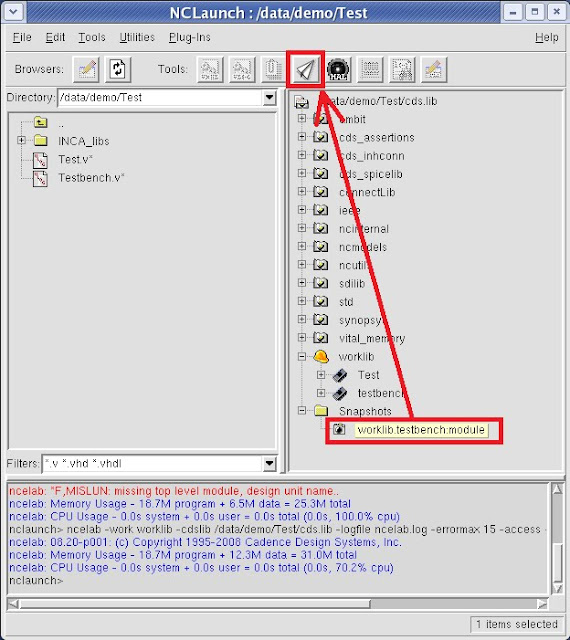

NC-Verilog下的三個工具:

ncvlog (Compiles the Verilog source files.)

ncelab (Elaborates the design and generates a simulation snapshot.)

ncsim (Simulates the snapshot.)

(1). 先產生Verilog程式,如下所示。

/////////////////////////////Schematic

module Test(a, b, c, d, En, Sel, f);

input a, b, c, d, En, Sel;

output f;

wire f;

wire g, h, i, j;

assign g = a | b;

assign i = g & En;

assign h = c | d;

assign j = h & En;

assign f = (Sel==1'b0) ? i : j;

endmodule

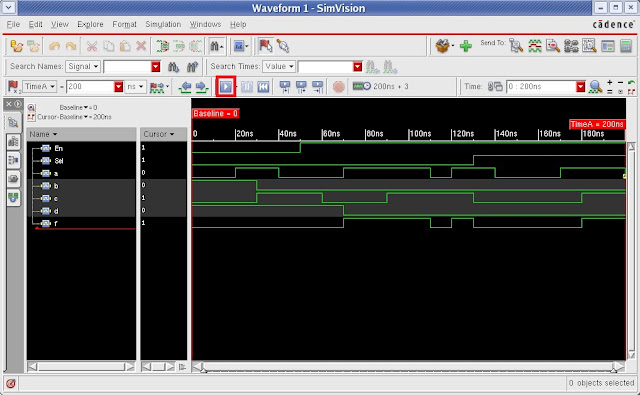

/////////////////////////////Testbench

module testbench;

reg a, b, c, d, En, Sel;

wire f;

Test UUT(

.a(a),

.b(b),

.c(c),

.d(d),

.En(En),

.Sel(Sel),

.f(f) );

initial

begin

a = 1'b0; // Time = 0

b = 1'b1;

c = 1'b0;

d = 1'b1;

En = 1'b0;

Sel = 1'b0;

#20; // Time = 20

a = 1'b1;

#10; // Time = 30

b = 1'b0;

c = 1'b1;

#10; // Time = 40

a = 1'b0;

#10; // Time = 50

En = 1'b1;

#10; // Time = 60

c = 1'b0;

#10; // Time = 70

a = 1'b1;

d = 1'b0;

#20; // Time = 90

c = 1'b1;

#20; // Time = 110

a = 1'b0;

#10; // Time = 120

a = 1'b1;

#10; // Time = 130

c = 1'b0;

Sel= 1'b1;

#10; // Time = 140

a = 1'b0;

#30; // Time = 170

a = 1'b1;

#10; // Time = 180

c = 1'b1;

#20; // Time = 200

a = 1'b0;

end

endmodule

(2). 在Linux作業系統中建立一個目錄,並將Schematic與Testbench,複製至目錄中。