(1) . 點選"Programmer"ICON。

(2). 點選"Hardware Setup"按鈕。(3). 使用滑鼠快點兩下Available hardware items欄位中的"USB-Blaster"選項,之後Currently selected hardware:就會修給為"USB-Blaster [USB-0]"選項,之後按"Close"結束設定。

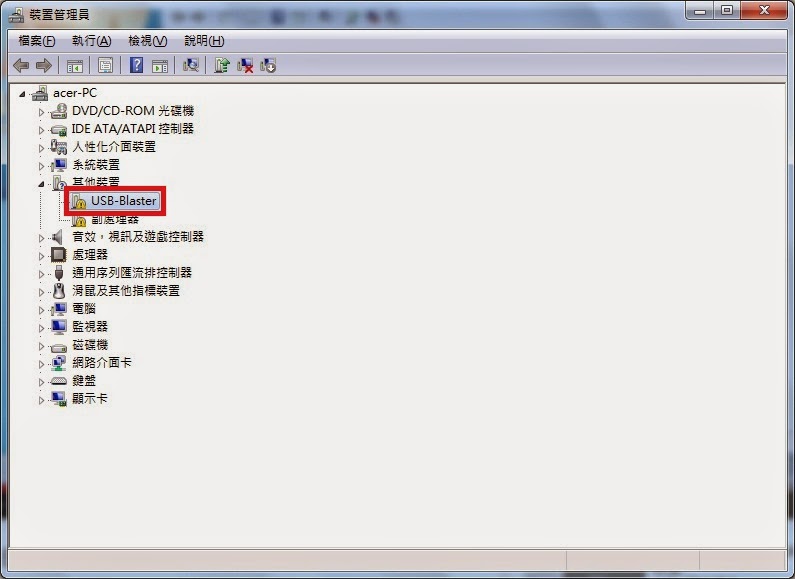

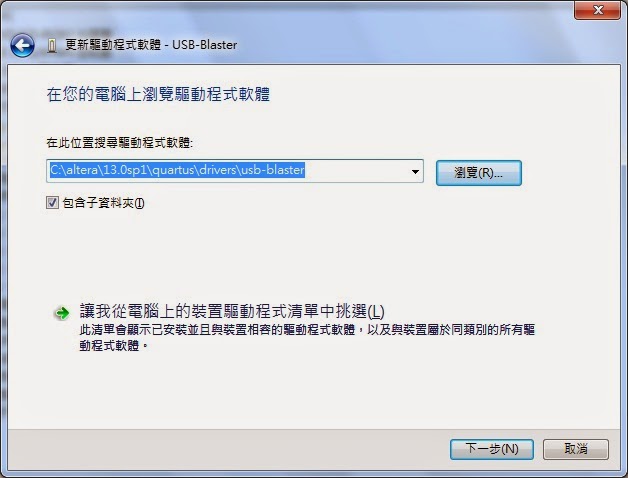

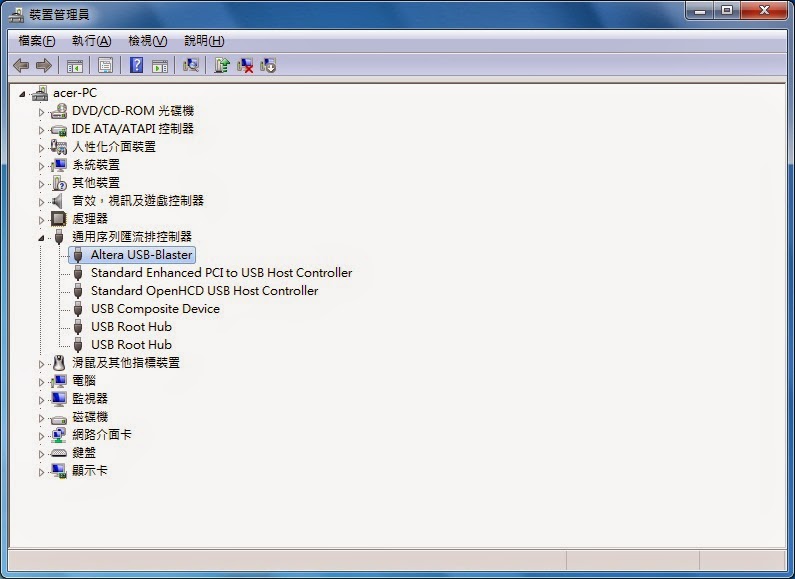

如果Available hardware items欄位中沒有看到"USB-Blaster"選項,煩請先安裝驅動程式。

(4). 按"Add File..."按鈕。

(5). 點選"xxx.jic"燒錄檔後,按"Open"。

(6). 依下圖所示點選"xxx.sof"圖示後,按"滑鼠右鍵" > "Edit" > "Delete",刪除xxx.sof圖示。

(7). 最後按"Start"按鈕後,開始燒錄,燒錄進度可看"Progress:"顯示的進度。