(1). 選擇"Physical View"顯示結果。

2016年11月24日 星期四

Lattice Diamond 3.8 - (6) 燒錄FPGA

(1). 選擇"Programmer"。

(2). 選擇欄位"Cable:"設定所使用的Download cable,之後在選擇"Port:",設定完成按"OK"。

(3). 在"File Name"欄位選擇"xxx_impl1.jed"檔。

(4). 先點選"JTAG Scam",連線FPGA之後再選擇"impl1.xcf"燒錄檔,最後點選"Program" 開始燒錄。

Lattice Diamond 3.8 - (5) 設定FPGA腳位與完整編譯

(1). 選擇"Spreadsheet View"。

(2). 產生"Spreadsheet View"標籤頁視窗。

(3). 在"Pin"欄位中選擇欲在FPGA信號輸出與輸入的IO腳位。

(4). 按"Save"存檔。

(5). 選擇"Process"標籤頁,使用"滑鼠左鍵"點選兩下"Export Files"開始完整編譯。

Lattice Diamond 3.8 - (4) 模擬

(1). 選擇"Simulation Wizard"。

(2). 選擇"Next >"。

(3). 在"Project name:"欄位中輸入模擬計畫的名稱後按"Next >"。

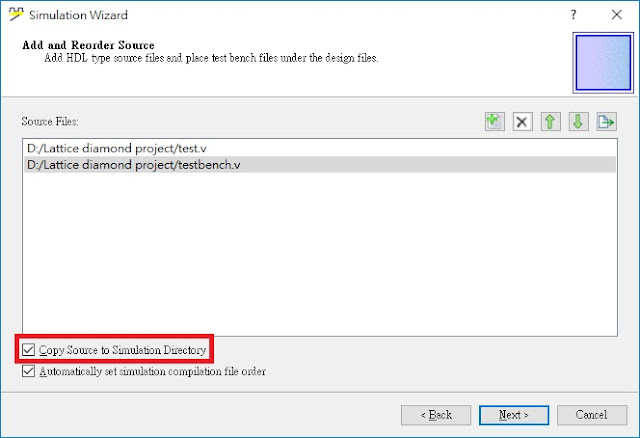

(4). 選擇"RTL"後按"Next >"。

(5). 在"Source Files:"欄位中可以看到數位電路程式(test.v)與模擬程式(testbench.v),勾選"Copy Source to Simulation Directory",會將test.v與testbench.v複製到新增模擬的檔案夾中,之後按"Next >"。

(6). 可以看到在"Simulation Top Module:"欄位中看到模擬程式為testbench.v,之後按"Next >"。

(7). 最後按"Finish"結束設定。

(8). 軟體會自動開啟"Active-HDL"並顯示結果。

Lattice Diamond 3.8 - (3) 新增Test bench

(1). 選擇"File List"標籤頁,之後再選擇"Input Files",按"滑鼠右鍵",選擇"Add" > "New File..."。

(2). 選擇"Verilog Files",之後在"Name:"欄位中輸入檔案名稱後按"New"。

(3). 輸入程式。

`timescale 1 ns/1 ns

module testbench;

reg a, b, c, d, En, Sel;

wire f;

Test UUT(

.a(a),

.b(b),

.c(c),

.d(d),

.En(En),

.Sel(Sel),

.f(f) );

initial

begin

a = 1'b0; // Time = 0

b = 1'b1;

c = 1'b0;

d = 1'b1;

En = 1'b0;

Sel = 1'b0;

#20; // Time = 20

a = 1'b1;

#10; // Time = 30

b = 1'b0;

c = 1'b1;

#10; // Time = 40

a = 1'b0;

#10; // Time = 50

En = 1'b1;

#10; // Time = 60

c = 1'b0;

#10; // Time = 70

a = 1'b1;

d = 1'b0;

#20; // Time = 90

c = 1'b1;

#20; // Time = 110

a = 1'b0;

#10; // Time = 120

a = 1'b1;

#10; // Time = 130

c = 1'b0;

Sel= 1'b1;

#10; // Time = 140

a = 1'b0;

#30; // Time = 170

a = 1'b1;

#10; // Time = 180

c = 1'b1;

#20; // Time = 200

a = 1'b0;

end

endmodule

(4). 點選"Save"存檔後,選擇"Process"標籤頁,使用"滑鼠左鍵"點選兩下"Lattice Synthesis Engine"開始編譯。

Lattice Diamond 3.8 - (2) 新增Verilog程式檔案與編譯

(1). 選擇"File List"標籤頁,之後再選擇"Input Files",按"滑鼠右鍵",選擇"Add" > "New File..."。

(2). 選擇"Verilog Files",之後在"Name:"欄位中輸入檔案名稱後按"New"。

(3). 輸入程式。

`timescale 1 ns/1 ns

module Test(a, b, c, d, En, Sel, f);

input a, b, c, d, En, Sel;

output f;

wire f;

wire g, h, i, j;

assign g = a | b;

assign i = g & En;

assign h = c | d;

assign j = h & En;

assign f = (Sel==1'b0) ? i : j;

endmodule

(4). 點選"Save"存檔。

(5). 選擇"Process"標籤頁,使用"滑鼠左鍵"點選兩下"Lattice Synthesis Engine"開始編譯。

Lattice Diamond 3.8 - (1) 新增Project

(1). 選擇"File" > "New" > "Project..."。

(2). 選擇"Next >"。

(3). 在"Name:"欄位中輸入計畫名稱,我這裡輸入"Teat",輸入完成選擇"Next >"。

在"Location:"為計劃檔案的所在位置,可以按"Browse..."選擇自己想存放的位置。

(4). 選擇"Next >"。

(5). 這裡需依照您所使用的FPGA型號設定,設定完成選擇"Next >"。

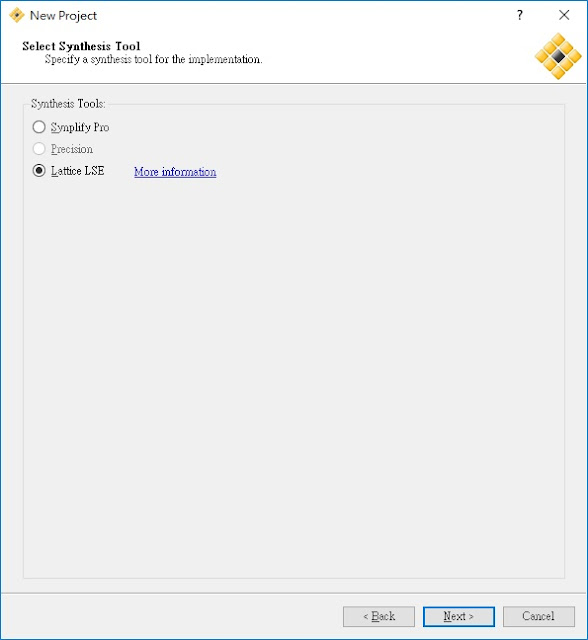

(6). 選擇合成的工具,我這裡選擇"Lattice LES"(Lattice Synthesis Engine,LES),設定完成選擇"Next >"。

(7). 完成設定,按"Finish"結束。

訂閱:

意見 (Atom)