使用S-EDIT設計電路:

增加Library :

C:\..\Tanner\Tanner Tools v16.3\Process\Generic_250nm\Generic_250nm_AnalogLib\Generic_250nm_AnalogLib.tanner

C:\..\Tanner\Tanner Tools v16.3\Process\Standard_Libraries\SPICE_Elements\SPICE_Elements.tanner

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

呼叫T-Sice模擬信號:

設定SPICE Simulation:

點選"Setup" > SPICE Simulation.

(1). General > Simulation Outputs > Enable Waveform Voltage Probing:

True

(2). General > File and Directory Names > Library File:

C:\..\Tanner\Tanner Tools v16.3\Process\Generic_250nm\Generic_250nm_Tech\Generic_250nm.lib TT

(必須加入TT)

(3). 勾選"Transient/Fourier Analysis",

Stop Time: 100ns

Maximum Time Step: 0.1ns

完成模擬後,使用S-EDIT,選擇File > Export > Export SPICE...,將設計好的電路轉成.spc檔.

~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

使用L-EDIT Layout電路:

(1). 新增專案,設定專案存檔路徑,選擇"TDB",並增加函示庫.

C:\..\Tanner\Tanner Tools v16.3\Process\Generic_250nm\Generic_250nm_Tech\Generic_250nm_TechSetup.tdb

(2). 增加函示庫,選擇Setup > Design... > Libraries,在Path欄位中選擇

C:\..\Tanner\Tanner Tools v16.3\Process\Generic_250nm\Generic_250nm_Tech\Generic_250nm_TechSetup.tdb

(3). 建立新的Cell,選擇 Cell > New...,修改名稱與上述S-EDIT創建名稱相同.

(4). 選擇Tools > SDL Navigator > Load Netlist,

在"Netlist"標籤欄中選擇Import Netlist(.spc)檔案,並勾選

Include substrate terminals of semiconductor devices in netlist

之後在"Layout"標籤欄中勾選

Add instances for missing subcircuits

Add instances of T-Cells for missing devices

Add missing I/O ports

Create New Ports

Layer: Metal1

Size: .35

Update parameters of T-cells

2017年3月29日 星期三

2017年3月23日 星期四

Quartus II 16.1 - (10) 快速Verilog程式除錯與模擬

依照上述每一次按"Start Compilation"後,需要經過Verilog程式編譯 > 電路合成 > 訊號模擬,需要花費很多時間,下列的步驟只有先分析電路後,直接做RTL模擬,加快程式除錯的時間。

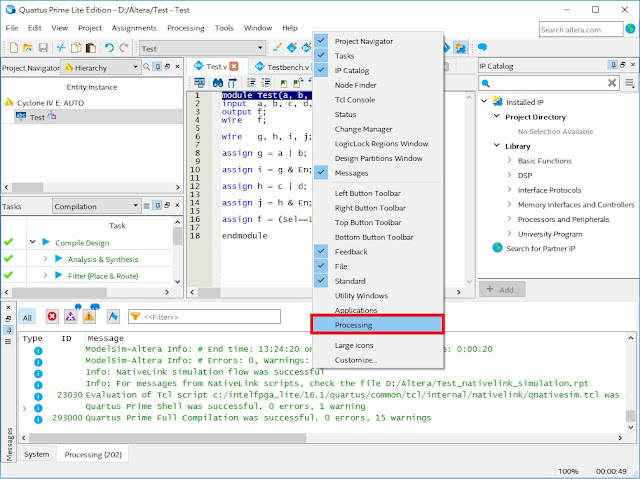

(1). 將滑鼠游標移至工具列,按"滑鼠右鍵",勾選"Processing"。

(2). 增加了工具列的ICON。

(3). 當模組電路與Test bench撰寫好後,點選"Analyze Current File",會將程式存檔,並進行電路分析。

(4). 電路分析沒有出現錯誤,如果有合成過,就點選"RTL Simulation",沒有合成過,就點選"Gate Level Simulation",此時軟體會開啟ModelSim。

依據上個步驟只有點選"Analyze Current File",分析設計的電路是否正確,哪這一步因該要點選"Gate Level Simulation"。

(5). 最後顯示其電路模擬的波形。

紅線: "x"狀態表示不定值。

藍線: "hi-z"狀態表示高阻抗。

綠線: 0、1狀態表示IO輸出值。

白色虛線: pu狀態表示外部模擬拉高電位。

訂閱:

意見 (Atom)