會發現載入錯誤的,導致無法使用ModelSim摸擬,將parameter參數傳遞的方式刪除又可以正常使用ModelSim摸擬。

電路:

module Test

#(parameter Width = 1)(

input [Width-1:0] a,

input [Width-1:0] b,

output [Width-1:0] c

);

assign c = a & b;

endmodule

Testbench:

module Testbench;

reg [7:0]a;

reg [7:0]b;

wire [7:0]c;

Test #(.Width(8)) DUT(

.a(a),

.b(b),

.c(c)

);

initial

begin

a = 8'h01;

b = 8'h00;

#100

a = 8'h02;

b = 8'h00;

#100

a = 8'h04;

b = 8'h00;

#100

a = 8'h08;

b = 8'h00;

#100

a = 8'h10;

b = 8'h00;

#100

a = 8'h20;

b = 8'h00;

#100

a = 8'h40;

b = 8'h00;

#100

a = 8'h80;

b = 8'h00;

#100

a = 8'h01;

b = 8'h01;

#100

a = 8'h02;

b = 8'h02;

#100

a = 8'h04;

b = 8'h04;

#100

a = 8'h08;

b = 8'h08;

#100

a = 8'h10;

b = 8'h10;

#100

a = 8'h20;

b = 8'h20;

#100

a = 8'h40;

b = 8'h40;

#100

a = 8'h80;

b = 8'h80;

#100

$finish;

end

endmodule

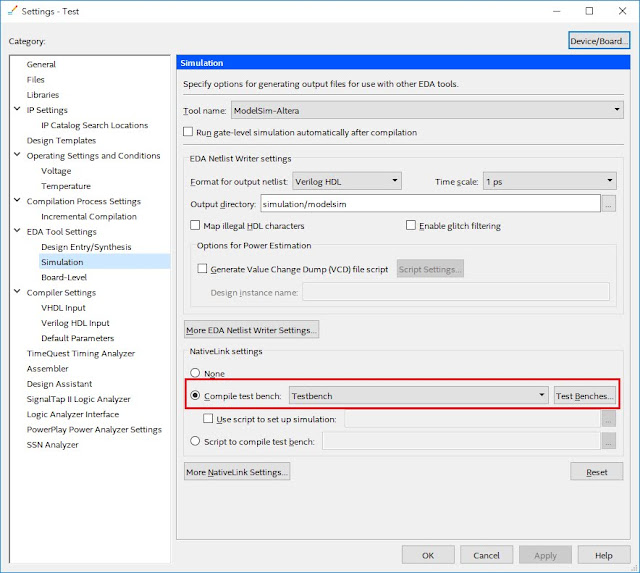

(3). 點選"EDA Tool Options",確認ModelSim-Altera欄位路徑後按"OK"。

(4). 滑鼠游標在工具列空白處按"滑鼠右鍵",勾選"Processing"。

(5). 編輯好電路與Testbench,按"Analyze Current File"進行分析與合成電路,

模擬前在Project的Top層圖示按"滑鼠右鍵" > "Settings...",

點選"Simulation",圈選"Compile test bench:"欄位,並加入之前所撰寫好的Testbench。

(6). 按"RTL Simulation"進行模擬。

(7). ModelSim可以正常載入並模擬。

沒有留言:

張貼留言