1. 點選"IP Catalog",增加IP Symbol。

2. 在"Search:"欄位中輸入"clock",尋找"Clocking Wizard"並點選。

3. 點選後可以開啟"Clocking Wizard "設定視窗。

4. 在"Input Frequenc(MHz)"欄位中輸入"50",此參數是因為開發板使用50MHz的震盪器。

5. 點選"Output Clocks"標籤頁,在"Output Clock"勾選需要輸出多少組頻率,我這裡勾選4組,之後在"Requested"欄位中,輸入所需要的頻率值,我這裡由上至下,輸入"200"、"100"、"50"、"25"。

6. 一般會在設計電路時,Reset會習慣使用低電位時動作,所以我這裡在"Reset Type"選擇"Active Low",設定完成按"OK"。

7. 按"OK"。

8. 按"Generate"。

9. 按"OK"。

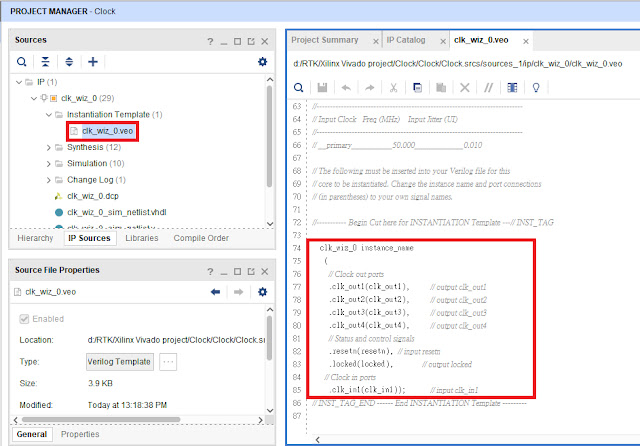

10. 選擇在Sources視窗的IP Sources標籤頁,點選開啟"Clk_Wiz_0.veo",複製IP 連接的IO port。

clk_wiz_0 instance_name

(

// Clock out ports

.clk_out1(clk_out1), // output clk_out1

.clk_out2(clk_out2), // output clk_out2

.clk_out3(clk_out3), // output clk_out3

.clk_out4(clk_out4), // output clk_out4

// Status and control signals

.resetn(resetn), // input resetn

.locked(locked), // output locked

// Clock in ports

.clk_in1(clk_in1)); // input clk_in1

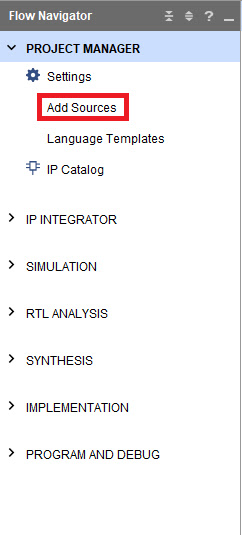

11. 增加設計電路檔案,在"Flow Navigator"視窗,點選"PROJECT MANAGER > Add Sources"。

12. 勾選"Add or create design sources"之後按"Next>"。

13. 點選"Create File"。

14. 在"File name:"欄位中,輸入source檔案名稱,這裡輸入"Clock",輸入完成按"OK"。

15. 按"Finish",增加source檔案。

16. 按"OK"。

17. 按"Yes"。

18. 在"Sources"視窗中的"Hierarchy"標籤頁中,開啟"Clock.v"檔,貼上IP 連接的IO port,並設定電路IO port的設定。

`timescale 1ns / 1ps

module Clock(

input clk_in1,

input resetn,

output clk_out1,

output clk_out2,

output clk_out3,

output clk_out4

);

clk_wiz_0 clk_wiz_0

(

// Clock out ports

.clk_out1(clk_out1), // output clk_out1

.clk_out2(clk_out2), // output clk_out2

.clk_out3(clk_out3), // output clk_out3

.clk_out4(clk_out4), // output clk_out4

// Status and control signals

.resetn(resetn), // input resetn

.locked(locked), // output locked

// Clock in ports

.clk_in1(clk_in1)); // input clk_in1

endmodule

19. 增加模擬電路檔案,在"Flow Navigator"視窗,點選"PROJECT MANAGER > Add Sources"。

20. 勾選"Add or create simulation sources"之後按"Next>"。

21. 點選"Create File"。

22. 在"File name:"欄位中,輸入source檔案名稱,這裡輸入"testbench",輸入完成按"OK"。

23. 按"Finish",增加simulation source檔案。

24. 按"OK"。

25. 按"Yes"。

26. 在"Sources"視窗中的"Hierarchy"標籤頁中,開啟"testbench.v"檔,設計模擬電路。

`timescale 1ns / 1ps

`define FLASH 1'b1

module testbench();

reg clk_in1;

reg resetn;

wire clk_out1;

wire clk_out2;

wire clk_out3;

wire clk_out4;

Clock uClouk(

.clk_in1 (clk_in1),

.resetn (resetn),

.clk_out1 (clk_out1),

.clk_out2 (clk_out2),

.clk_out3 (clk_out3),

.clk_out4 (clk_out4)

);

initial

begin

clk_in1 = `FLASH;

forever #5 clk_in1 =~clk_in1;

end

initial

begin

resetn = 0;

#100;

resetn = 1;

#8000000 $finish;

end

endmodule

27. 開始模擬,在"Flow Navigator"視窗,點選"SIMULATION > Run Simulation",跳出視窗後點選"Run Behavioral Simulation"。

28. 顯示模擬視窗,如下圖所示,可以看到OUTPUT輸出四種不同頻率。

沒有留言:

張貼留言