1. 先將"FPGA board"的JTAG使用"xilinx USB Cable"與PC連接。

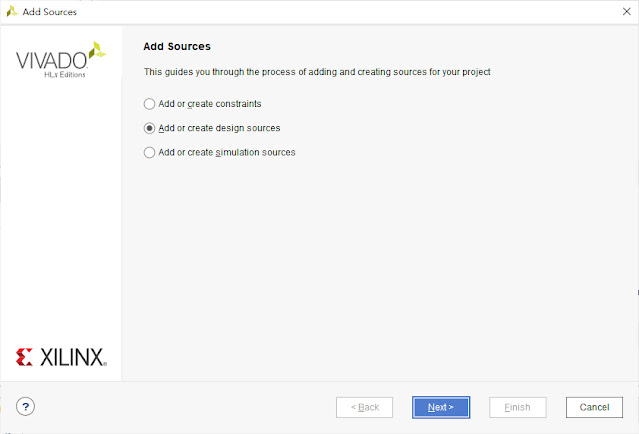

2. 增加設計電路檔案,在"Flow Navigator"視窗,點選"PROJECT MANAGER > Add Sources"。

3. 勾選"Add or create design sources"之後按"Next>"。4. 點選"Create File"。

5. 在"File name:"欄位中,輸入source檔案名稱,這裡輸入"bl_led",輸入完成按"OK"。

7. 按"OK"。

8. 按"Yes"。

9. 在"Sources"視窗中的"Hierarchy"標籤頁中,開啟"Bl_led.v"檔,撰寫設計電路。

`timescale 1ns / 1ps

module bl_led(

input sys_clk,

input rst_n,

output reg[3:0] led

);

parameter max_cnt = 32'd49999999;

reg[31:0] timer_cnt;

always@(posedge sys_clk or negedge rst_n)

begin

if(!rst_n)

begin

timer_cnt <= 32'd0;

end

else

begin

if(timer_cnt < max_cnt)

timer_cnt <= timer_cnt +32'd1;

else

timer_cnt <= 32'd0;

end

end

always@(posedge sys_clk or negedge rst_n)

begin

if(!rst_n)

begin

led <= 4'b0000;

end

else

begin

if(timer_cnt == max_cnt)

led <= ~led;

else

led <= led;

end

end

endmodule

10. 點選"IP Catalog",增加IP Symbol。

12. 在"General Options"標籤頁,"Number of Probes"欄位設定為"2",表示需要量測2組訊號。

13. 在"Probe_Ports(0..1)的標籤頁,PROBE0的Probe Width[1..4096]欄位設"32",PROBE1的Probe Width[1..4096]欄位設"4",這部分的設定是依據設計電路需要量測波形的bit數,設定完成按"OK"。

14. 按"OK"。

15. 按"Generate"。

16. 按"OK"。

17. 選擇在Sources視窗的IP Sources標籤頁,點選開啟"ila_0.veo",複製IP 連接的IO port。

18. 在"Sources"視窗中的"Hierarchy"標籤頁中,開啟"bl_led.v"檔,貼上IP 連接的IO port,並設定電路IO port的設定。

`timescale 1ns / 1ps

module bl_led(

input sys_clk,

input rst_n,

output reg[3:0] led

);

parameter max_cnt = 32'd49999999;

reg[31:0] timer_cnt;

always@(posedge sys_clk or negedge rst_n)

begin

if(!rst_n)

begin

timer_cnt <= 32'd0;

end

else

begin

if(timer_cnt < max_cnt)

timer_cnt <= timer_cnt +32'd1;

else

timer_cnt <= 32'd0;

end

end

always@(posedge sys_clk or negedge rst_n)

begin

if(!rst_n)

begin

led <= 4'b0000;

end

else

begin

if(timer_cnt == max_cnt)

led <= ~led;

else

led <= led;

end

end

ila_0 ila_0_inst (

.clk(sys_clk), // input wire clk

.probe0(timer_cnt), // input wire [31:0] probe0

.probe1(led) // input wire [3:0] probe1

);

endmodule

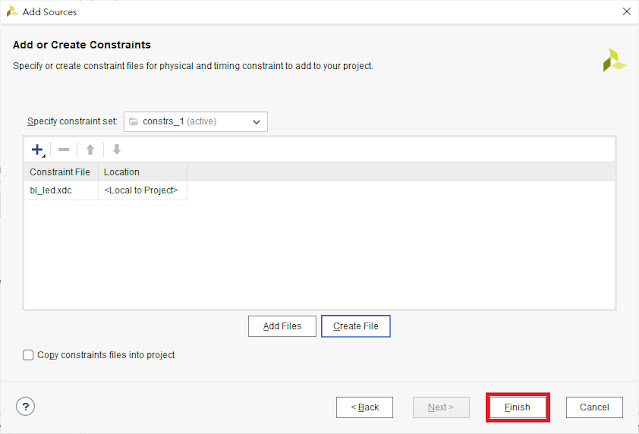

19. 增加限制條件檔案,在"Flow Navigator"視窗,點選"PROJECT MANAGER > Add Sources"。

20. 勾選"Add or create constraints"之後按"Next>"。21. 點選"Create File"。

22. 在"File name:"欄位中,輸入constraint檔案名稱,這裡輸入"bl_led",輸入完成按"OK"。

23. 按"Finish",增加constraint檔案。

24. 在"Sources"視窗中的"Hierarchy"標籤頁中,開啟"bl_led.xdc"檔,並設定IO port的限制條件。

############## NET - IOSTANDARD ##################

set_property CFGBVS VCCO [current_design]

set_property CONFIG_VOLTAGE 3.3 [current_design]

#############SPI Configurate Setting##################

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

set_property CONFIG_MODE SPIx4 [current_design]

set_property BITSTREAM.CONFIG.CONFIGRATE 50 [current_design]

#############clock Setting#########################

create_clock -period 20 [get_ports sys_clk]

set_property IOSTANDARD LVCMOS33 [get_ports {sys_clk}]

set_property PACKAGE_PIN Y18 [get_ports {sys_clk}]

#############reset Setting##########################

set_property IOSTANDARD LVCMOS33 [get_ports {rst_n}]

set_property PACKAGE_PIN F20 [get_ports {rst_n}]

#############LED Setting###########################

set_property PACKAGE_PIN F19 [get_ports {led[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[0]}]

set_property PACKAGE_PIN E21 [get_ports {led[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[1]}]

set_property PACKAGE_PIN D20 [get_ports {led[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[2]}]

set_property PACKAGE_PIN C20 [get_ports {led[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[3]}]

25. 產生bitstream(.bin)檔,在"Flow Navigator"視窗,點選"PROJECT MANAGER > PROGRAM AND DEBUG",按"滑鼠右鍵",點選"Bitstream Settings..."。

26. 在"Project Settings > Bitstream"視窗中,將"-bin_file"打勾,之後按"OK"。

27. 產生.bin檔,點選"Generate Bitstream"。

28. 按"Yes"。

29. 按"OK"。

30. 需要稍微等待一下,產生.bin檔。

31. 產生.bin檔程序結束,按"OK"。

32. 連線FPGA開發板,在"Flow Navigator"視窗,點選"PROJECT MANAGER > PROGRAM AND DEBUG > Open Hardware Manager > Open Target",跳出視窗後,點選"Auto Connect"。

33. 燒錄.bin檔,在"Flow Navigator"視窗,點選"PROJECT MANAGER > PROGRAM AND DEBUG > Open Hardware Manager > Program Device",跳出視窗後,點選"xc7a35t_0"(此為開發板上的FPGA型號)。

34. 按"Program",開始燒錄。

35. 按"Run trigger for this ILA core",開始讀取波形。

沒有留言:

張貼留言